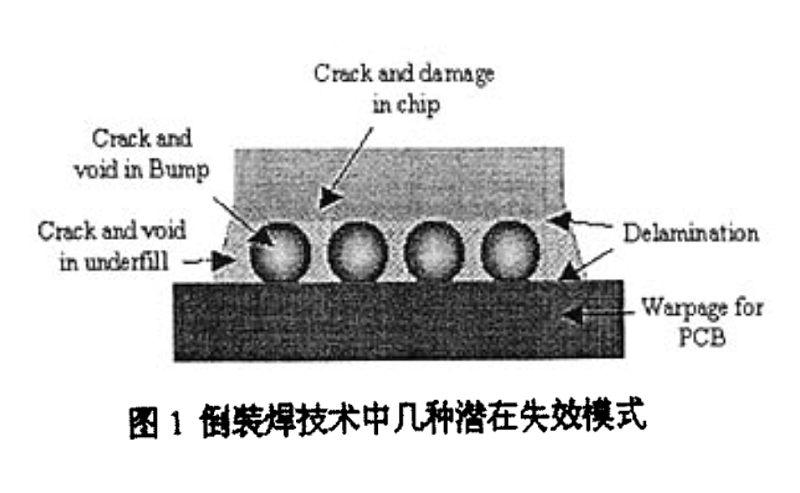

同其他封裝形式(shì)相比,倒(dǎo)裝焊技術在電子製造業領域應用更為廣泛,這是因為(wéi)它在尺寸、性能、機(jī)動性、可靠性和成本等方麵的優勢,這是一種更加先進的封裝技術。在倒裝焊技術中,帶焊點的芯片可以直(zhí)接焊接到低值有機(jī)基板上,如FR-4印刷線路板,然後采用填充物進行密封,與塑封器件(jiàn)類似,填充(chōng)料密封可以顯著(zhe)地減少芯片(piàn)和基板熱(rè)膨脹係數(CTE)不(bú)匹配而產生剪切應力,從(cóng)而大大提(tí)高焊點的疲勞壽命(mìng)。盡管如此,在密(mì)封填(tián)充物、芯片和基板間的界麵仍然是主(zhǔ)要影響可靠性的問題所在,如芯(xīn)片裂紋、填充物裂紋和分層等等。裂紋在金屬間化合物(IMC)中很容易延伸並擴張,金屬間化(huà)合物通(tōng)常(cháng)是在焊點與底層金屬化層(UBM)之間,所以,裂紋和分層影響到焊點疲勞壽命的提高。圖I所示是(shì)倒裝焊技(jì)術領域中幾種常見的潛在失效模式。

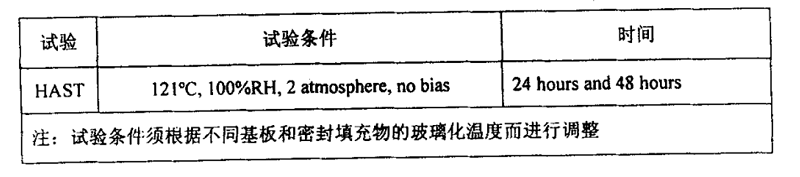

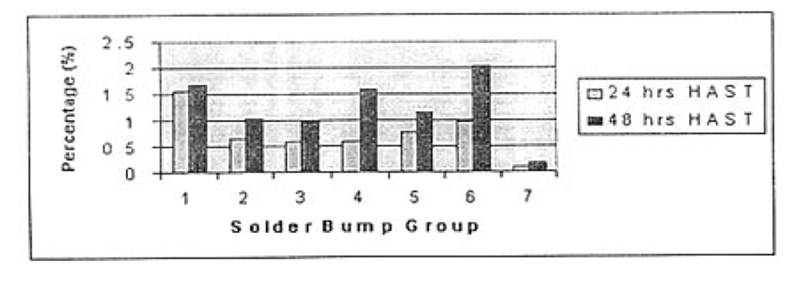

在本文(wén)中(zhōng),HAST作為一個加速環境試(shì)驗,用於快速評估倒裝焊接在FR-4 基板上麵(miàn)陣分布焊點的(de)可靠性。該試驗(yàn)主要是通過加速侵蝕(shí)過程(chéng),從而大大縮(suō)短了可靠性評估時間。本次試驗樣品在經過本文設計的HAST試驗後(見表1), 進行了相關的可靠性分析和(hé)失效(xiào)分析。試驗結果(guǒ)說明HAST能夠作為一個有效的可靠性試驗評價工具用於倒(dǎo)裝焊技術領域。

設計成雛菊鏈狀試(shì)驗電路的芯片(5。0x5。0mm)組裝到FR4基板上,該芯片采用電鍍基焊點(diǎn){。藝沉積共晶焊點(63Sn/37Pb),在芯(xīn)片表麵濺射阻擋(dǎng)層Ti-W(1000A)和Cu(4000A), 焊點的平均高度為100μm, 焊點間(jiān)距為(wéi)450um,焊(hàn)點麵陣分(fèn)布數量為I0x10(如圖 2所示)。密封填充(chōng)物繞芯片邊沿90℃ 注入(rù),然後固化。

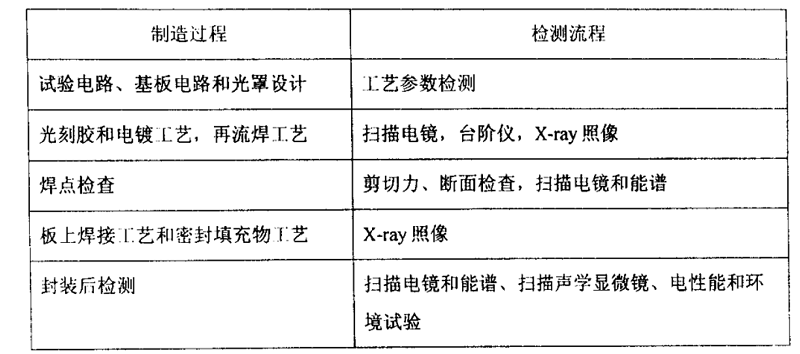

所有試驗(yàn)樣品都要進行電性能測試和掃描聲學顯微鏡(SAM)檢查,以(yǐ)進行HAST試驗前後的比較。試驗樣品的製造過程和檢測流程見表2所示。

對倒裝焊技術而言,密封填充物和(hé)芯片或基板間的分(fèn)層和焊點可靠性一(yī)直是一個特別重要的課題。對塑封型器件的可靠性評價,多年來-直將雙85試(shì)驗作為標準評價試驗工具。本文(wén)提出采用加(jiā)速環境(jìng)試驗如HAST,對倒裝焊接在FR4基板上麵陣分布的焊點進行可靠性評價,試驗結果表明可以代替雙85試驗,將是用於倒裝焊技術領域的-一(yī)個有效的可靠性試驗工具。

文章源於:網絡

400電話